Oñemoheñóivo ciencia ha tecnología, marandu ha momarandu tecnología iñambue ára ha ára, tapichakuéra rembiaporã ojeruréva komputadórape g̃uarã yvateve ohóvo. Ojoajúvo, umi hardware oñeikotevëva umi equipo comunicación informática avei yvate ohóvo, PCB ha'eháicha equipo electrónico umi producto de base, grado de precisión de gama alta odetermina rendimiento opavave equipo de comunicación informática oñemohu'ãva.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.

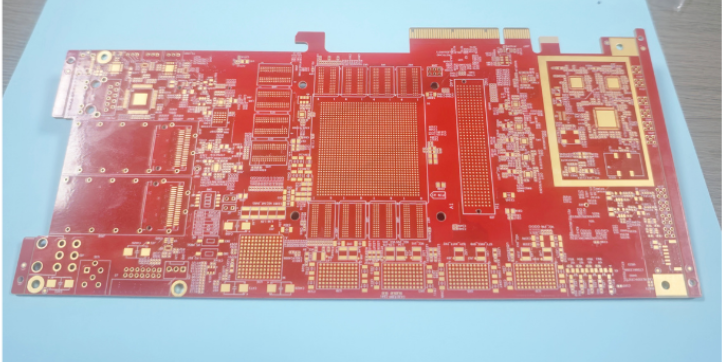

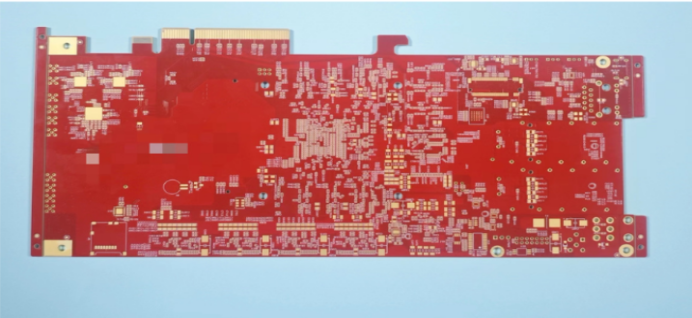

Ko’áĝa, Sanxis ogueru ndéve peteĩ PCB FPGA oñembopya’éva ojeporúva tembipuru’i computación ha red aceleración rehegua rendimiento yvateguápe.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.

FPGA heꞌise Field-Programmable Gate Array, haꞌevahína peteĩ tipo circuito semiconductor integrado rehegua ohejáva umi diseñador-pe oprograma ha omohenda jey hag̃ua lógica hardware rehegua ojejapo rire. Umi FPGA ojepuru jepi diseño electrónico ha prototipo-pe oikuaveꞌe rupi flexibilidad ha ikatuha ojeitera pyaꞌe.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.

FPGA iporãiterei ikatúgui oñeprograma jey ombohovái hag̃ua opaichagua tekotevẽ, haꞌehína peteĩ mbaꞌeporã tuicha mbaꞌeva umi circuito integrado específico aplicación rehegua (ASIC) ojejapóva mbaꞌeteépe g̃uarã ha ndaikatúiva oñemoambue upe rire.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.

Peteĩ FPGA estructura básica oguereko unidad entrada/salida programable, bloque lógico configurable, módulo reloj digital jesarekorã, RAM bloque embotado, recurso enrutamiento rehegua, núcleo duro dedicado incorporado ha unidad funcional incorporada subyacente. Pe proceso diseño rehegua peteĩ FPGA rehegua oike diseño algoritmo rehegua, simulación ha diseño código rehegua, depuración nivel tablero rehegua, umi diseñador omopyendahápe peteĩ arquitectura algorítmica oñemopyendáva umi tekotevẽ añeteguáva rehe, oipuru tembipuru EDA omoheñói hag̃ua solución diseño rehegua térã código HDL, oasegura diseño ombohováiha umi mbaꞌe ojejeruréva práctico código rupive simulación, ha ipahápe ojejapo depuración nivel tablero-pegua ojehecha hag̃ua mbaꞌeichaitépa ombaꞌapo añetegua ojegueru rire umi archivo iñimportánteva chip FPGA-pe.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.

FPGA ojepuru hetaiterei opaichagua mbaꞌe haꞌeháicha circuito digital diseño, sistema comunicación rehegua, taꞌãngamýi ñemboguata ha hetave mbaꞌe. Ojekuaa ikatu haguére omaneha interfaces velocidad yvate, procesamiento señal digital ha flexibilidad diseño-pe, ohejáva ojeadapta pyaꞌe umi mbaꞌe pyahu ojejeruréva térã ñemoambue tecnología-pe.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.

Ko mba’ekuaarã ñemboheraguapy ta’angápe oĩta ambue pyahúpe. Emboguejy pe enlace oĩva iguype relee hag̃ua hetave mbaʼe.

Ñe’ẽpoty ha ñe’ẽpoty ñemoarandu.